Na komunikacione linije za DATA i CLOCK tesko moze da se stavlja ta "pasiva" za spustanje napona. Relativno su brzi signali tu u pitanju i svako unosenje nekih rednih otpornosti a jos gore paralelnih kapacitivnosti (od zenerice) ce skroz poremetiti oblik signala i poremetiti komunikaciju.

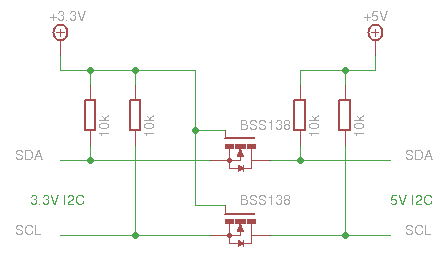

Bar za ove DATA i CLOCK linije se to radi sa prostim level-shifter, ovako nesto (nema veze sto pise da je za I2C, to je predvidjeno i za dvosmernu komunikaciju):

Za VDD je isto prosto, mora da se obezvedi 3.3V stabilisani izvor, recimo sa nekim low-drop regulatorom.

Jedino za VPP (za programiranje) ne znam kako to resiti. Tu je nezgodno zato sto se ima 3 naponska nivoa, 0-5-12V a to treba pretvoriti u 0-3-12V.

Ne znam da li bi to moglo da prodje tako kako jeste, bez modifikacije, nece sigurno da se osteti PIN jer inace trpi 12V. Treba pogledati DS i videti koliki je naponski prag za ulazak u programski mod.

Inace postoji mogucnost za low-voltage programiranje na nekim PIC-evima, bez 12V, ali je to u ovoj situaciji od male pomoci zato sto se mora setovati jedan flag u konfiguraciji PIC-a ali on moze samo sa 12V da se setuje pa tek onda udje nadalje u mod za LV programiranje. Kasnije se "ne dira" taj flag i tako ostane u tom modu.